As the benefits of continually shrinking transistor sizes diminish, researchers increasingly focus on system-technology co-optimization as a path to continued performance gains in computing. Yi Ren, Baokang Peng, and Chenhao Xue, along with colleagues at their institutions, present a new automated framework called Orthrus that tackles the complex challenge of simultaneously optimising both system architecture and underlying hardware. Orthrus uniquely bridges the information gap between these design levels, efficiently exploring a vast design space to identify optimal solutions, and prioritises critical components based on system-level demands. This innovative approach achieves significant improvements, demonstrably reducing delay by 12. 5% at constant power and saving 61. 4% power at constant delay compared to existing methods, effectively establishing new benchmarks in system-technology co-optimization.

Automated Design-Process Co-Optimization for ICs

Scientists developed a framework to automate and improve design-technology co-optimization (DTCO) for integrated circuit (IC) design. As semiconductor technology scales down, the interaction between circuit design and manufacturing processes becomes increasingly critical, demanding a simultaneous optimization of both. This framework explores both circuit architectures and manufacturing parameters to achieve better performance, power efficiency, and yield. A key component of this work involves automatically extending standard cell libraries, the fundamental building blocks of digital circuits, allowing for more optimized designs.

Machine learning (ML) plays a central role, with predictive models forecasting circuit performance based on design and process parameters. Bayesian optimization and other ML-based techniques efficiently search the vast design and process space, while surrogate models accelerate the optimization process by replacing computationally expensive simulations. The system also employs graph matching and hashing to identify and reuse optimized designs, and hypervolume optimization to balance multiple performance goals. The framework systematically explores design and process options, builds ML models to predict performance, and uses ML-based algorithms to identify optimal solutions. It then automatically generates circuit layouts based on these designs and verifies their performance, delivering improved IC performance, reduced design time, lower manufacturing costs, and enabling advanced semiconductor technologies.

Automated System-Technology Co-Optimization for VLSI Circuits

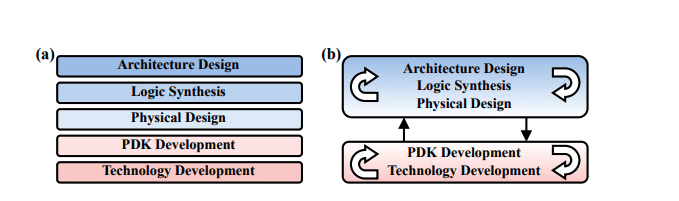

Scientists engineered Orthrus, an automated framework to address limitations in system-technology co-optimization (STCO) for very large-scale integration (VLSI) circuits. Recognizing the challenges of optimizing expansive full-stack VLSI flows, the team created a system that synergizes optimizations at both the system and technology levels, prioritizing efficient exploration of the design space and bridging information gaps across design hierarchies. At the system level, Orthrus prioritizes optimization of critical standard cells using statistics gathered from system-level analysis, focusing computational resources on the most impactful components. The system guides technology-level optimization by leveraging the normal directions of the Pareto frontier, efficiently explored using Bayesian optimization, ensuring technology-level adjustments align with overall system goals and maximize performance gains.

At the technology level, the team leverages system-aware insights to optimize standard cell libraries. Scientists implemented a neural network-assisted enhanced differential evolution algorithm to efficiently optimize technology parameters, intelligently searching the parameter space for optimal performance characteristics. Experiments on 7nm technology demonstrate that Orthrus achieves a 12. 5% reduction in delay at constant power and 61. 4% power savings at constant delay, establishing new Pareto frontiers in STCO.

Orthrus Optimizes VLSI Design with Dual-Loop Approach

Scientists present Orthrus, a novel automated framework designed to optimize system performance by bridging the gap between system-level requirements and technology innovations in VLSI design. Recognizing the limitations of traditional design methodologies as Moore’s Law reaches its limits, Orthrus employs a dual-loop approach to synergize system-level and technology-level optimizations, addressing the challenge of navigating expansive cross-layer design spaces. At the system level, the framework prioritizes optimization of critical standard cells using system-level statistics, effectively guiding technology-level optimization along directions that maximize performance gains. Experiments conducted on 7-nanometer technology demonstrate that Orthrus achieves a significant 12.

5% reduction in delay at constant power consumption and a substantial 61. 4% reduction in power consumption while maintaining constant delay. These results establish new Pareto frontiers in system-technology co-optimization, demonstrating a breakthrough in performance and efficiency. The team meticulously optimized parameters including compressor tree types, carry-propagate adder types, clock periods, synthesis efforts, placement utilization ratios, and critical technology parameters like gate work functions and fin dimensions. The framework’s success stems from its ability to leverage system-aware insights to optimize standard cell libraries, utilizing a neural network-assisted enhanced differential evolution algorithm to efficiently tune technology parameters.

Cross-Layer Optimisation Yields Significant Gains

Scientists present Orthrus, a novel automated framework for system-technology co-optimization, addressing a critical need in sustaining scaling trends within the VLSI industry. By effectively bridging the information gap between system requirements and underlying technology innovations, Orthrus simultaneously optimizes designs at both the system and technology levels. Experimental results, conducted using 7nm technology, demonstrate that Orthrus achieves a significant 12. 5% reduction in delay at constant power and a substantial 61. 4% power saving at constant delay, surpassing the performance of existing approaches.

These improvements are further quantified by a 33. 2% increase in hypervolume, establishing new boundaries for Pareto optimality in cross-layer design. Future research aims to broaden the applicability of Orthrus by extending its support to encompass a wider range of architectures and process technologies, thereby enhancing its versatility and impact on future VLSI designs.