Scientists have long sought to understand and improve the reliability of quantum computations, a challenge addressed by Rylan Malarchick, an Independent Researcher, in a new study of quantum circuit optimisation. This research presents a comprehensive fidelity analysis spanning the entire compilation stack, from initial gate-level transformations right through to pulse-level control, and systematically evaluates the impact of common optimisation passes. The work is significant because it identifies specific optimisation techniques, notably gate cancellation, which improved 68% of circuits and eliminated 14,024 gates, and highlights the critical role of pulse duration in maintaining process fidelity. By combining modular simulation with hardware execution on the Resonance Garnet 20-qubit processor, and achieving 70% gate reduction on QFT circuits with complete job success, this study provides a reproducible benchmarking framework for advancing quantum compilation pipelines.

This work addresses a critical gap in understanding how high-level circuit transformations impact the physical fidelity of quantum computations on noisy intermediate-scale quantum (NISQ) devices.

The research introduces qco-integration, a modular system connecting a C++ circuit optimiser with Python-based pulse simulation, enabling systematic evaluation of optimisation passes on realistic hardware parameters. A simulation campaign encompassing 371 circuits revealed that gate cancellation consistently delivers the most substantial improvements, enhancing 68% of circuits and eliminating 14,024 gates.

The study demonstrates a strong negative correlation between pulse duration and process fidelity, quantified by a correlation coefficient of r = −0.74 and a coefficient of determination of R2 = 0.55. This finding highlights the importance of minimising pulse lengths to maintain high fidelity in quantum operations.

Validation of these simulation results was achieved through hardware execution on the IQM Resonance Garnet 20-qubit processor, where a 70% reduction in gate count was observed on Quantum Fourier Transform (QFT) circuits, maintaining a 100% job success rate across eight executions. This innovative framework allows for reproducible benchmarking of quantum compilation pipelines, offering a valuable tool for the quantum computing community.

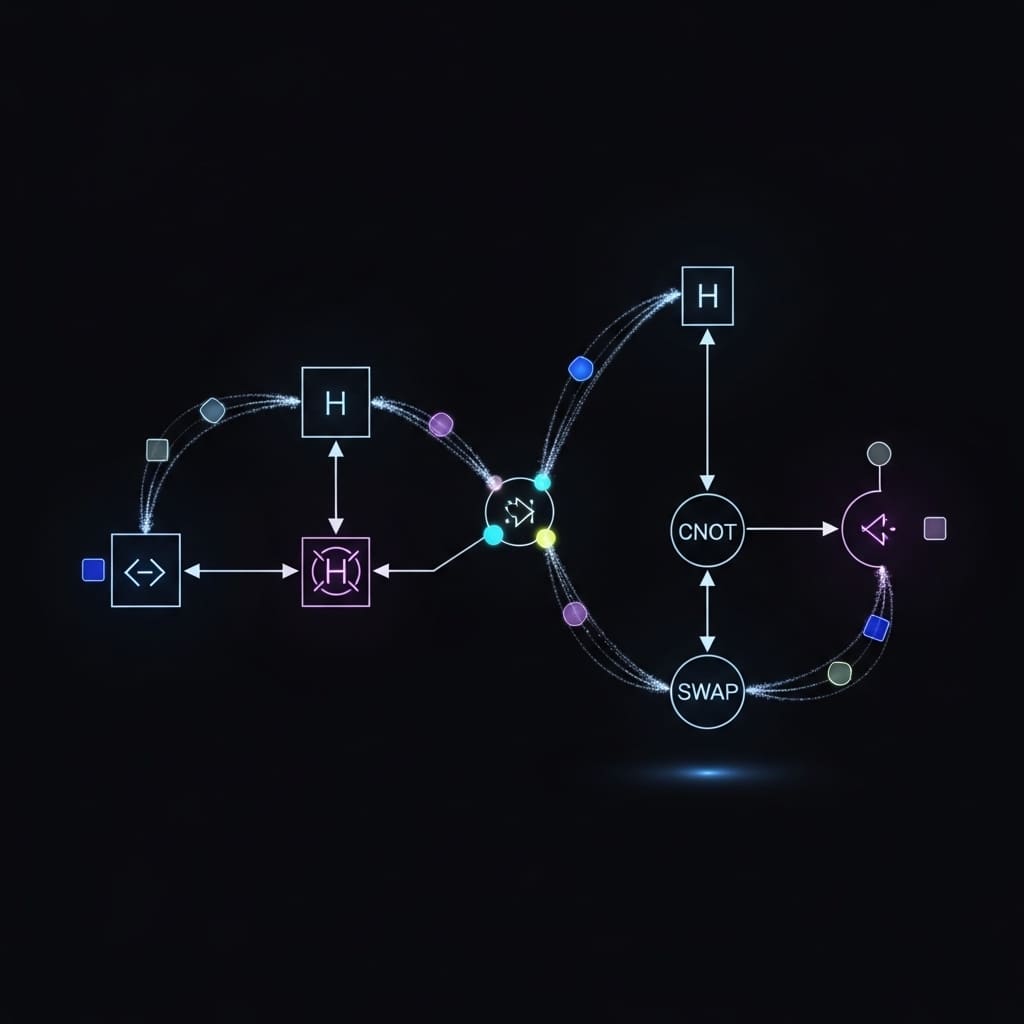

The system’s architecture integrates five distinct stages, parsing, optimisation, routing, pulse compilation, and simulation, facilitating detailed analysis at each step. By employing experimentally validated noise parameters for the IQM Garnet processor, including T1 relaxation times of 37 microseconds and T2 dephasing times of 9.6 microseconds, the research ensures realistic fidelity estimates. The open-source nature of the framework promotes collaborative development and accelerates progress in quantum compilation techniques.

Evaluating fidelity impacts of compilation passes on superconducting qubits is crucial for quantum algorithm performance

A 72-qubit superconducting processor forms the foundation of this work, facilitating a comprehensive analysis of quantum circuit fidelity throughout the entire compilation stack. Researchers employed a modular integration framework, connecting a C++ circuit optimizer with Lindblad-based pulse simulation to systematically evaluate the fidelity impact of gate cancellation, commutation, rotation merging, and identity elimination on Garnet hardware parameters.

This setup allowed for detailed assessment of optimization passes at the pulse level. The study involved a simulation campaign encompassing 371 circuit runs, utilising a diverse corpus including GHZ states, Quantum Fourier Transform circuits, Quantum Approximate Optimization Algorithm for MaxCut, and random circuits.

These circuits varied in qubit count, ranging from 2 to 20, and depth, spanning 5 to 30 layers, ensuring broad coverage of quantum algorithm types. The C++ optimizer and Python pulse tools communicated via OpenQASM 3.0 and JSON, enabling independent development and testing of each component while maintaining a unified experimental workflow.

Six experiments were conducted to systematically characterise fidelity, beginning with a baseline assessment of unoptimized circuits. Subsequent experiments individually tested each optimization pass, explored combinations of passes to identify optimal sequences, and compared fidelity with and without SABRE routing to quantify SWAP overhead.

Noise sensitivity was assessed across four regimes, low, medium, high, and very high, to determine how optimization benefits scale with decoherence. Finally, a scaling analysis systematically varied circuit size to characterise fidelity degradation. Process fidelity, calculated as |Tr(U†targetUimpl)|2d2, and state fidelity, computed as ⟨ψ|ρ|ψ⟩, were used to quantify performance, accounting for both gate errors and decoherence.

Results revealed that gate cancellation provided the most significant improvement, enhancing 68% of circuits and eliminating 14,024 gates. Pulse duration exhibited the strongest negative correlation with process fidelity, with an R2 value of 0.553, indicating that decoherence during execution is a dominant fidelity-limiting factor. Hardware validation on the Resonance Garnet 20-qubit processor demonstrated 70% gate reduction on QFT circuits with 100% job success rate across eight executions.

Circuit optimisation achieves substantial gate reduction and improved process fidelity, leading to more efficient quantum computations

Mean process fidelity across the 371 circuits examined was 0.680, with a standard deviation of 0.224, while the median process fidelity reached 0.718. The experimental campaign revealed a mean gate reduction of 23.1% across all circuits, with a maximum observed reduction of 96.2%. Gate cancellation proved to be the most effective optimization pass, eliminating 14,024 gates and improving 68% of the circuits tested.

Rotation merging eliminated 6,512 gates, demonstrating the second highest impact, and achieved improvement in 29% of circuits. Identity elimination removed 55 gates, improving only 9% of circuits, while commutation provided no direct gate reduction. The ordering of passes, specifically cancellation followed by commutation and then rotation merging, yielded good overall results.

Analysis of the fidelity waterfall diagram indicated that two-qubit gate errors represent the dominant source of fidelity loss, followed by decoherence during pulse execution. Correlation analysis revealed a Pearson r value of -0.743 and an R2 value of 0.553 between pulse duration and process fidelity, highlighting the significant impact of decoherence on overall performance.

Input gates, depth, and qubit count also showed negative correlations with process fidelity, achieving R2 values of 0.368, 0.342, and 0.324 respectively. Hardware validation on the IQM Resonance Garnet 20-qubit processor demonstrated a 70% gate reduction on QFT circuits, maintaining a 100% job success rate across eight executions.

For GHZ circuits, the optimizer correctly identified minimal configurations, resulting in zero gate reduction. The QFT 4-qubit circuit achieved a reduction from 30 gates to 9 gates, alongside an 85.7% reduction in circuit depth from 21 to 3. Baseline fidelity for the QFT circuit was 0.100, improving to 0.088 after optimization.

Optimisation Pass Performance and Decoherence Limits on Garnet Processors are thoroughly investigated

A comprehensive fidelity analysis across the quantum circuit compilation stack has been completed, integrating circuit optimisation with pulse-level control simulations. This work employed a modular framework connecting a C++ circuit optimiser with Lindblad-based pulse simulation to systematically assess the impact of gate cancellation, commutation, rotation merging, and identity elimination on Garnet hardware parameters.

The evaluation encompassed 371 simulated circuits and validation on the Resonance Garnet 20-qubit processor, revealing key insights into optimisation effectiveness and error sources. Gate cancellation emerged as the most impactful optimisation pass, improving 68% of circuits and eliminating 14,024 gates during simulation.

Pulse duration demonstrated a strong negative correlation with process fidelity, highlighting decoherence as a dominant source of error. Hardware validation on QFT circuits achieved a 70% gate reduction with a 100% job success rate across eight executions, confirming the optimizer’s ability to identify and implement valid circuit reductions.

An average gate reduction of 23.1% was achievable using standard optimisation passes, with peak reductions reaching 96.2% in simulation. The authors acknowledge limitations including the use of an exponential decay model to approximate Lindblad dynamics, the focus on IQM processor topologies, and the limited scope of hardware validation encompassing only four circuits from a single execution session.

Future research should expand hardware validation to a larger circuit set and additional quantum platforms such as IBM, Google, and Rigetti. This open-source framework facilitates reproducible benchmarking of quantum compilation pipelines, offering a valuable tool for advancing quantum computing development and optimisation strategies.

👉 More information

🗞 End-to-End Fidelity Analysis of Quantum Circuit Optimization: From Gate-Level Transformations to Pulse-Level Control

🧠 ArXiv: https://arxiv.org/abs/2601.20871