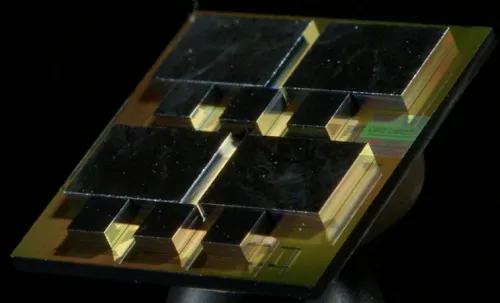

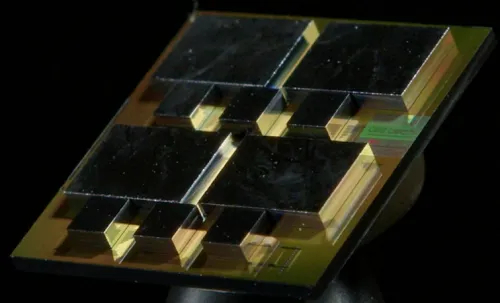

At the ISSCC yesterday, CEA-List and CEA-Leti presented an electro-optical router with dynamic, frame-level optical routing integrated with CMOS control logic – an enabler for chiplet-based optical networking.

Their paper, “A 3.19pJ/bit Electro-Optical Router with 18ns Setup Frame-Level Routing and 1-6 Wavelength Flexible Link Capacity for Photonic Interposers”, demonstrates an electro-optical router implemented in 28 nm CMOS on a photonic interposer, capable of establishing optical paths in 18 nanoseconds.

It dynamically selects one-to-six wavelengths per link, and achieves an energy efficiency of 3.19 pJ/bit with an active area of just 0.007 mm² per link.

The router integrates optical switching, routing control, Serdes, and clocking logic directly with silicon photonics.

The result is a dynamically routed optical interconnect that operates at nanosecond timescales, enabling optical communication across centimeter-scale interposers with responsiveness previously limited to short electrical links.

It supports frame-level routing, allowing optical paths to be established and torn down on demand, and adjusts link capacity dynamically by selecting between one and six wavelengths, according to application needs. This flexibility enables efficient use of optical bandwidth, while maintaining ultra-low latency.

Analogue drivers, combined with standard-cell-based SerDes and clocking circuits, enable dense integration of optical endpoints close to compute and memory resources.

By bringing dynamic, ultra-low-latency optical networking into the package, the technology opens possibilities for HPC, AI accelerators, and data-intensive systems.

Rather than forcing all data to reside near compute cores to minimise electrical routing costs, dynamically routed optical links allow architects to treat memory and compute resources across the interposer as part of a unified, high-reach fabric without sacrificing latency or energy efficiency