Key Takeaways

Variation becomes a bigger problem in multi-die assemblies with TSVs and hybrid bonding.

Multi-modal approaches are required to test these devices.

AI can play a significant role in distinguishing between yield-killing and nuisance variations and significantly reduce false positives.

New methods for interconnecting devices using through-silicon vias (TSVs) and hybrid bonding in stacked chips are exhibiting high levels of process variation, which complicates traditional defect inspection routines. Because these advanced packaging architectures lack maturity, identifying the best inspection method is more challenging than it was in the past.

The great diversity of packaging approaches increases the numbers and types of defects that need to be characterized, including voids, residues, film discontinuities, and feature misalignments. That, in turn, impacts the long-term reliability of 2.5D and 3D multi-chiplet assemblies.

Variation is a big part of the problem. Even the most tried and true approaches to optical inspection are complicated by previous processes and the variability they cause. “Substantial die-to-die process variation in chiplet packaging using silicon interposers and fan-out technologies reduces the reliability of conventional golden-die and die-to-die inspection approaches,” said Woo Young Han, product marketing director at Onto Innovation. While quite accurate, finding a perfect “golden” die is difficult due to variations in the assembly process.

Even so, there are new tools that deliver faster results and greater distinction between actual and nuisance defects. “Machine learning–driven defect detection and automatic defect classification (ADC) offer improved robustness, enabling more accurate defect identification with fewer false or nuisance detections,” added Han.

Today’s solutions

There is an abundance of potentially yield-killing defects that can impact the performance and reliability of advanced packages. These include opens, shorts, and defective bumps caught during solder bump inspection. In wafer-to-wafer and die-to-wafer Cu-Cu hybrid bonding, voids, copper oxide residues, and misaligned bumps or pads across a wafer may significantly impact yield.

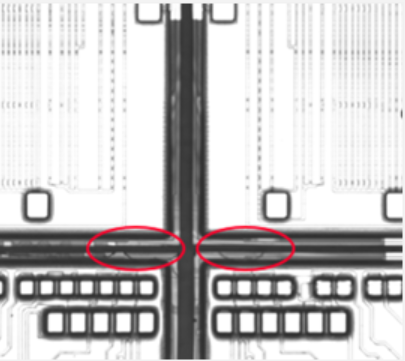

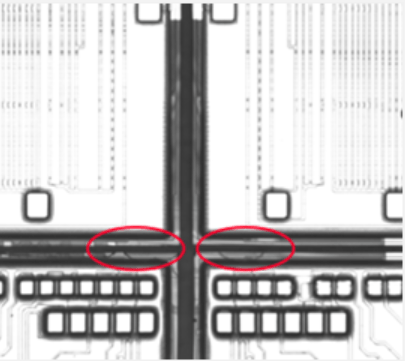

Fig. 1: High-speed IR inspection can catch cracks at any layer during die-to-wafer hybrid bonding including pick-and-place and die sawing. Source: Onto Innovation

High-speed infrared inspection enables inner die crack detection with 100% full wafer coverage at high throughput. Its flexible, multi-resolution imaging design helps to ensure reliable crack identification across all layers in the D2W process.

Engineers are employing different inspection tools — based on optical/IR automated inspection (AOI), electron beam (e-beam), X-ray, and acoustic modalities – to non-destructively test TSV structures. Automated optical/IR methods are the fastest, and some companies are speeding the process further by developing more powerful sensors or using multiple sensors on each tool. AOI can detect a variety of defects successfully. An iNEMI survey of substrate providers, OSATs, EMS, and inspection equipment manufacturers highlighted the top defect types caught by AOI equipment in high-volume manufacturing of advanced substrates. [1] Such defects include laminate/ABF substrate base material defects, shorts, copper nodules, missing copper (i.e., pin holes), surface nicks, too-wide or too-narrow copper widths, and via misalignment.

And because connecting platforms in advanced packages have only recently grown from two to five main levels of interconnect (from the dies to the substrate), the straightforward separation of chip fabrication from PCB assembly is blurring with front-end processes such as TSV and hybrid bonding, which do not belong solely to the fab or to the OSAT. For now, TSVs are fabricated in foundries like TSMC under front-end cleanroom conditions, though this could change in the coming years as TSVs and hybrid bonding become more common.

Taking a closer look at the steps involved in building 2.5D and 3D devices helps illuminate the best paths to finding, characterizing, and eliminating both random and systematic defects from the assembly process.

Through-silicon vias

TSVs are proving essential to miniaturization and multi-function semiconductor packages. The goal of TSV flows is to create low-stress, void-free TSVs on a consistent basis. TSV technology enables high-density vertical interconnection from chip-to-chip, which significantly reduces the three-dimensional size of the end device. The shorter interconnect lengths compared to long wire bonds also improve data propagation speed, lowering the device’s power consumption and improving the reliability of the system. This is why TSV technology is crucial to the success of 3D technologies.

The small and complicated features of TSVs give rise to different defect types. Defects can form during any of the TSV process steps, which include lithography patterning followed by deep reactive ion etching (DRIE), oxide liner deposition, barrier metal deposition, copper seed, copper electrochemical deposition (plating), CMP, and cleaning steps.

The reactive ion etch (RIE) process and metal deposition steps must be fully optimized to create smooth vias that achieve the desired metal step coverage and low overall resistance. After the TSV cavity is etched, a conformal oxide layer is deposited by PECVD along the via sidewalls to prevent copper from permeating the silicon.

Automated process control must capture changing conditions inside the PECVD chamber. “Plasma physics is not a linear process, so you can get much better process control by modeling something like film accumulation on the chamber walls, and you can also model how the process and equipment evolve over time,” said Jon Herlocker, vice president and general manager of software analytics at Cohu. “Every time you run a batch through the PECVD chamber, you get some amount of accumulation on the chamber walls, and other changes. The AI model can predict what the chamber is going to look like for the next run, so you can tweak your parameters before you even see the feedback.”

Following oxide PECVD, engineers deposit a thin metal barrier such as TaN or TiN using sputtering or atomic layer deposition (ALD), followed by copper fill. Whether voids form inside TSVs depends on the deposition processes and the aspect ratio of the via (depth: opening). Deposited layers must be thin, uniform and conformal around the TSV opening.

Following plating, any voids in the copper can result in elevated electrical resistance, decreased mechanical strength, or even device failure. Additionally, if there is sufficient queue time and the wafers are exposed to the environment, copper oxide will form after CMP. Other prominent structural defects to watch out for include non-uniform deposition and incomplete filling, which can degrade performance or cause long-term reliability risk.

“Through silicon via (TSV) technology is the most critical process in interposer and HBM fabrication. The greatest inspection challenges include organic residues such as polyimide or photoresist remaining on the TSV. During the plating process, copper interior voids can form, whereas the CMP process can create TSV dents at the Cu pad edge,” said Onto’s Yu.

Optical inspection faces challenges in illuminating organic remnants. “Organic residue is transparent and cannot be seen by either brightfield or darkfield inspection,” he said. “Copper voids cannot be detected with conventional optical inspection methods because light cannot penetrate through metal material. TSV dents often appear with color variation, which makes it difficult to separate the dent from a nuisance defect. As a result, customers have to trade off between capture rate and nuisance rate.”

Non-destructive infrared-based illumination inspection technology can see through non-metal materials to detect buried defects with a proven sub-micron sensitivity.

Electron-beam (e-beam) inspection tools have the sensitivity to capture submicron defects, but because e-beam operates by line-of-sight, it can only detect surface defects and very shallow defects inside features. However, e-beam tools offer high-contrast defect detection, and multibeam e-beam inspectors, such as those offered by ASML, address the longstanding throughput concerns associated with e-beam systems. In production fabs, e-beam tools are most often used in defect review stations and classification that follow wafer-level defect inspection with AOI tools.

There is a growing need to detect hidden defects in 3D stacks. A widely used inspection method for detecting buried defects is scanning acoustic microscopy (SAM). “Sensitivity of SAM can be down to 10µm,” said Yu. “The main drawback is potential contamination since the process includes immersing the wafer in water.

One approach taken by Nordson Test & Inspection involves spinning the wafer at high speed while using a waterfall transducer to provide non-immersion scanning, minimizing the risk of contamination or false-bond indications. Resolution is a function of the transducer frequency — higher frequency (up to 230 MHz) increases resolution.

Acoustic wafer inspection effectively detects voids at different depths into bonded wafers. It is especially good at detecting delamination and cracks. “One of the big things that is changing is the need for more resolution,” said Bryan Schackmuth, senior product line manager at Nordson Test & Measurement. “Rotational scan, rather than a raster scan, allows us to get a lot of data a lot faster than previously, and that resolution is absolutely critical.”

Acoustic inspection can zero in on the outer dimension of the wafer to detect edge defects, as well, providing higher contrast and resolution for that defined scan. Throughput on these systems is further boosted by a dry-in/dry-out multi-chamber design.

In addition, X-ray inspection is used to detect internal, hidden defects based on density differences, including solder joint misalignment in Cu pillars or bumps. “It tends to be used for fully automated leading-edge wafer processing, where the process steps can be more aggressive, and the cost of disruption to the line is more significant,” said John Wall, compound semiconductor business product manager at Bruker.

Intricacies of hybrid bonding

Hybrid bonding, which joins metal and dielectrics on two wafers, is gaining traction in advanced packaging because it offers the shortest vertical connection between dies of similar or different functionalities, as well as better thermal, electrical, and reliability results.

Hybrid bonding is ultra-sensitive to contamination. Because of the hardness of the SiO2 or SiCN dielectrics, any particle can disrupt the planar surface, causing large interfacial voids. In fact, that is one of the advantages to hybrid bonding with organic dielectrics. They are softer than inorganic films and can absorb nano-scale particles rather than bridging over them. Hybrid bonding with organics also tolerates rougher surfaces than oxide-oxide bonds.

“Successfully scaling hybrid bonding into high-volume manufacturing requires addressing challenges related to defect control, alignment precision, thermal management, wafer warpage, material compatibility, and process throughput,” said Alice Guerrero, principal applications engineer at Brewer Science.

Because wafer manufacturing process steps are carried out at different temperatures and produce spatially inhomogeneous device patterns, some stress often builds up around the device features. Voids, cracks, and surface roughness can produce localized stress that affects the performance and lifetime of the manufactured modules.

Defects in stacks and packages

Optical inspection remains the workhorse technology for finding surface defects going into hybrid bonding. “Before the bonding step, high-sensitivity automated optical inspection (AOI) is used to detect sub-micron surface defects, which may lead to bonding voids and delamination,” said Yu. “After bonding, AOI equipped with high-speed infrared technology is used to detect voids, cracks, and delamination between dielectric materials, enabled by IR’s ability to see through silicon and dielectric materials.”

In 2.5D and 3D-ICs, there is a persistent need to detect hidden defects at various interfaces. For this reason, a combination of X-ray, acoustic, and automated IR inspection is used in conjunction with electrical tests using voltage/thermal contrast. This physical/electrical combination is necessary because the most damaging defects could be electrically active but have subtle physical differences.

Each inspection method has its strengths and limitations. X-ray metrology and X-ray CT are essential for viewing defects in the 50nm and below range. X-ray transmits through the device and can detect defects in fully stacked or packaged devices. It can also find copper/copper non-uniformities at bonded interfaces.

X-ray defect inspection provides more than physical attributes. “XRDI is quite sensitive to strain fields and stacking errors, producing exact values of stress, composition, and thickness of defects,” said Bruker’s Wall. Unlike IR inspection, X-ray can image metals. Localized delaminations and voids are a product of stresses and mismatches in CTE of materials, which also causes warpage.

Like X-ray, acoustic inspection is effective at detecting delaminations, cracks and voids.

“X-ray is really geared toward density changes and looking at solder balls and metal traces. Acoustic is very complementary with X rays,” said Nordson’s Schackmuth. As mentioned previously, acoustic inspection tools are being optimized to prevent potential contamination from a process employing deionized water. “In the traditional method, where you immerse the wafer, you could get what’s called ingression of water into the layers.” Continuous scanning enabled by wafer rotation and a waterfall approach minimizes exposure while attaining the higher throughput needed for HVM.

Acoustic wafer inspection is being employed at multiple process steps. One example is temporary bonding, where a wafer is bonded to a carrier wafer during processes like extreme wafer thinning and later bonded to another substrate. “We might check the temporary bond because it’s critical for the processing that there aren’t defects at that layer. A delamination between the substrate and the wafer will cause somewhat of a blister or a bump in the wafer. If you’re doing a mechanical processing, those have a tendency to kind of explode, and you’ll get a breakout of the wafer,” said Schackmuth. When the temporary bond is removed and a wafer is bonded to another substrate, acoustic inspection is again performed.”

Where AI/ML comes in

Artificial intelligence (AI) is proving especially useful at distinguishing real from nuisance defects. “AI algorithms are used to generate a synthetic defect library based on nominal patterns, and they also help remove color variations for more accurate defect classification,” said Onto’s Yu. “With AI algorithms, the system can improve real defect capture rates while reducing nuisance rates.”

As inspection methods continually advance in resolution, problems with false or nuisance defects require a multipronged approach. This includes a combination of traditional automatic defect classifiers and AI/ML-based ADC classification. There are several ways to separate nuisance from real defects. “One common approach is to select the best optical mode to enhance real defect signals while depressing nuisance signals. Traditional ADC classifiers that use defect attributes can also provide effective separation,” said Yu.

“Wafer warpage can create height differences between neighboring dies, causing parts of the wafer to fall outside of the system’s optical depth of focus,” Yu added. “This results in defocus-related nuisance defects during inspection and leads to a higher nuisance rate. ”The latest AOI systems address this by using contour mapping and real-time height-tracking functions to keep the wafer at its target focus position throughout inspection.

AI/ML-based automated defect classification is more powerful than earlier versions, especially when it comes to meeting high accuracy requirements and reducing the amount of engineering time that goes into analysis.

Yu explains how AI algorithms are used to generate a synthetic defect library, based on nominal patterns, while also helping to remove color variations for more accurate defect classification.

“The limitations of AI adoption include situations where the available training dataset is not sufficient. Although AI requires fewer essential data than traditional ADC, the AI model still needs a meaningful volume of data to train effectively,” said Yu. “Another limitation is process iteration. If the process changes too quickly, a trained AI model may become outdated and require frequent retraining.”

ML also plays a role in improving acoustic inspection results. “We’re generating images, and traditionally we’ve used a threshold to analyze those images. So if a pixel is bright, above a certain threshold, it’s a defect. But with the complex structures of today’s parts, it’s no longer possible to capture the defects using that simple threshold type analysis,” said Schackmuth. To remedy this problem, AI/ML can combine inspection at the same points on the wafer, but across several process levels. However, it requires training on real defects. “We can teach it to identify real defects through a learning process. It will develop a model based on that, which we can use to do the analysis,” said Schackmuth.

Conclusion

As 3D processes for TSVs, hybrid bonding, and stacking in general improve, the inspection side is rapidly improving to better distinguish nuisance from real defects among optical/IR, acoustic, and X-ray technologies. All tools are advancing on the resolution front, and AI/machine learning is enabling faster and more accurate defect classification and process control as well as reduced engineering time.

Reference

Feng Xue, “AOI Pattern Detection Study for Fine Pitch Advanced Substrate,” ICEP 2023 Proceedings, WA1-2. https://ieeexplore.ieee.org/document/10129720

Related Articles

What’s Next For Through-Silicon Vias

Metrology Under Pressure: Detecting Defects In Fine-Pitch Hybrid Bonding