Jaeger, H. & Haas, H. Harnessing nonlinearity: predicting chaotic systems and saving energy in wireless communication. Science 304 (5667), 78–80. https://doi.org/10.1126/science.1091277 (2004).

Pati, S. P. et al. Real-time information processing via volatile resistance change in scalable protonic devices. Commun. Mat. 5 (1). https://doi.org/10.1038/s43246-024-00621-1 (2024).

Jaeger, H. The “echo state” approach to analysing and training recurrent neural networks (2010).

Maass, W., Natschläger, T. & Markram, H. Real-time computing without stable states: a new framework for neural computation based on perturbations. Neural Comput. 14 (11), 2531–2560. https://doi.org/10.1162/089976602760407955 (2002).

Abe, Y. et al. Highly-integrable analogue reservoir circuits based on a simple cycle architecture. Sci. Rep. 14 (1). https://doi.org/10.1038/s41598-024-61880-z (2024).

Moon, J. et al. Temporal data classification and forecasting using a memristor-based reservoir computing system. Nat. Electron. 2 (10), 480–487. https://doi.org/10.1038/s41928-019-0313-3 (2019).

Nishioka, D. et al. Edge-of-chaos learning achieved by ion-electron–coupled dynamics in an ion-gating reservoir. Sci. Adv. 8 (50). https://doi.org/10.1126/sciadv.ade1156 (2022).

Hochstetter, J. et al. Avalanches and edge-of-chaos learning in neuromorphic nanowire networks. Nat. Commun. 12 (1). https://doi.org/10.1038/s41467-021-24260-z (2021).

Usami, Y. et al. In-materio reservoir computing in a sulfonated polyaniline network. Adv. Mat. 33(48). https://doi.org/10.1002/adma.202102688 (2021).

Indiveri, G. Computation in neuromorphic analog VLSI systems. In Neural Nets WIRN Vietri-01. Persp. Neur. Comp. (eds. Tagliaferri, R., Marinaro, M.) 3–20. https://doi.org/10.1007/978-1-4471-0219-9_1 (2002).

Nguyen, D. A., Tran, X. T. & Iacopi, F. A review of algorithms and hardware implementations for spiking neural networks. J. Low Power Electron. Appl. 11 (2), 23. https://doi.org/10.3390/jlpea11020023 (2021).

Misra, J. & Saha, I. Artificial neural networks in hardware: a survey of two decades of progress. Neurocommun 74 (1–3), 239–255. https://doi.org/10.1016/j.neucom.2010.03.021 (2010).

Auge, D., Hille, J., Mueller, E. & Knoll, A. A survey of encoding techniques for signal processing in spiking neural networks. Neur Proces Lett. 53 (6), 4693–4710. https://doi.org/10.1007/s11063-021-10562-2 (2021).

Javanshir, A., Nguyen, T. T., Mahmud, M. P. & Kouzani, A. Z. Advancements in algorithms and neuromorphic hardware for spiking neural networks. Neural Comput. 34 (6), 1289–1328. https://doi.org/10.1162/neco_a_01499 (2022).

Bouvier, M. et al. Spiking neural networks hardware implementations and challenges: A survey. ACM J. Emer. Tech. Comp. Syst. (JETC). 15 (2), 1–35. https://doi.org/10.1145/3304103 (2019).

Maass, W. Networks of spiking neurons: the third generation of neural network models. Neural Netw. 10 (9), 1659–1671. https://doi.org/10.1016/S0893-6080(97)00011-7 (1997).

Gupta, A. & Long, L. N. Character recognition using spiking neural networks. IEEE Int. Conf. Neural Netw. 46, 53–58. https://doi.org/10.1109/ijcnn.2007.4370930 (2007).

Escobar, M., Masson, G. S., Vieville, T. & Kornprobst, P. Action recognition using a bio-inspired feedforward spiking network. Int. J. Comp. Vis. 82 (3), 284–301. https://doi.org/10.1007/s11263-008-0201-1 (2009).

Meftah, B., Lezoray, O. & Benyettou, A. Segmentation and edge detection based on spiking neural network model. Neur Proc. Lett. 32 (2), 131–146. https://doi.org/10.1007/s11063-010-9149-6 (2010).

Zheng, H., Wu, Y., Deng, L., Hu, Y. & Li, G. Going deeper with directly-trained larger spiking neural networks. Proc. AAAI Conf. Artif. Intell. 35 (12), 11062–11070. https://doi.org/10.1609/aaai.v35i12.17320 (2021).

Tavanaei, A. & Maida, A. Bio-inspired multi-layer spiking neural network extracts discriminative features from speech signals. Lecture Notes Comp. Sci. 899–908. https://doi.org/10.1007/978-3-319-70136-3_95 (2017).

Loiselle, S., Rouat, J., Pressnitzer, D. & Thorpe, S. J. Exploration of rank order coding with spiking neural networks for speech recognition. Proce. 2005 IEEE Int. Joint Conf. Neural. Netw. (2005). https://doi.org/10.1109/ijcnn.2005.1556220 (2005).

Ghosh-Dastidar, S. & Adeli, H. Improved spiking neural networks for EEG classification and epilepsy and seizure detection. Integ Comput.-Aided Eng. 14 (3), 187–212. https://doi.org/10.3233/ica-2007-14301 (2007).

Kasabov, N. et al. Evolving spiking neural networks for personalised modelling, classification and prediction of spatio-temporal patterns with a case study on stroke. Neurocomput. 134, 269–279. https://doi.org/10.1016/j.neucom.2013.09.049 (2014).

Furber, S. B., Galluppi, F., Temple, S. & Plana, L. A. The spinnaker project. Proc. IEEE. 102 (5), 652–665. https://doi.org/10.1109/JPROC.2014.2304638 (2014).

Akopyan, F. et al. TrueNorth: design and tool flow of a 65 MW 1 million neuron programmable neurosynaptic chip. IEEE Trans. Comput.-Aided Des. Integ Circ. Syst. 34 (10), 1537–1557. https://doi.org/10.1109/tcad.2015.2474396 (2015).

Benjamin, B. V. et al. Neurogrid: a mixed-analog-digital multichip system for large-scale neural simulations. Proc. IEEE 102(5), 699–716. https://doi.org/10.1109/jproc.2014.2313565 (2014).

Davies, M. et al. Loihi: A neuromorphic Manycore processor with on-chip learning. IEEE Mic. 38 (1), 82–99. https://doi.org/10.1109/mm.2018.112130359 (2018).

Thakur, C. S. et al. Large-scale neuromorphic spiking array processors: a quest to mimic the brain. Front. Neurosci. 12 https://doi.org/10.3389/fnins.2018.00891 (2018).

Pehle, C. et al. The BrainScaleS-2 accelerated neuromorphic system with hybrid plasticity. Front. Neurosci. 16 https://doi.org/10.3389/fnins.2022.795876 (2022).

Mead, C. Neuromorphic electronic systems. Proc. IEEE. 78 (10), 1629–1636. https://doi.org/10.1109/5.58356 (1990).

Armbrust, M. et al. A view of cloud computing. Commun. ACM. 53 (4), 50–58. https://doi.org/10.1145/1721654.1721672 (2010).

Shi, W., Cao, J., Zhang, Q., Li, Y. & Xu, L. Edge computing: vision and challenges. IEEE Int. Thin J. 3 (5), 637–646. https://doi.org/10.1109/jiot.2016.2579198 (2016).

Dowrick, T., McDaid, L. & Hall, S. Fan-in analysis of a leaky integrator circuit using charge transfer synapses. Neurocomput 314, 78–85. https://doi.org/10.1016/j.neucom.2018.06.065 (2018).

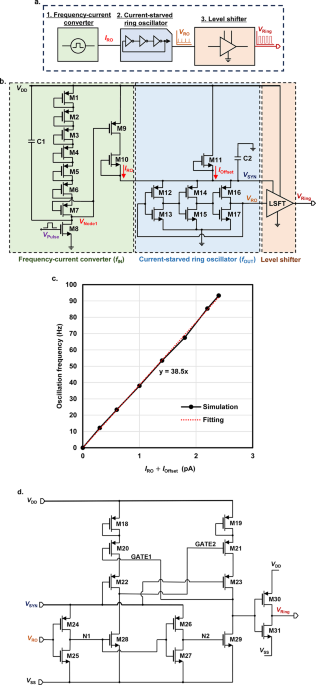

Mondal, A. J., Talukdar, J. & Bhattacharyya, B. K. Estimation of frequency and amplitude of ring oscillator built using current sources. Ain S Eng. J. 11 (3), 677–686. https://doi.org/10.1016/j.asej.2020.01.006 (2020).

Joubert, A., Belhadj, B., Temam, O. & Héliot, R. Hardware spiking neurons design: analog or digital? In The 2012 Int. Joint Conf. Neural. Netw. (IJCNN), 1–5. https://doi.org/10.1109/IJCNN.2012.6252600 (2012).

Indiveri, G., Chicca, E. & Douglas, R. A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity. IEEE Trans. Neural Netw. 17 (1), 211–221. https://doi.org/10.1109/tnn.2005.860850 (2006).

Chen, X. et al. CMOS-based area-and-power-efficient neuron and synapse circuits for time-domain analog spiking neural networks. Appl. Phys. Lett. 122 (7). https://doi.org/10.1063/5.0136627 (2023).

Yajima, T. Ultra-low-power switching circuits based on a binary pattern generator with spiking neurons. Sci. Rep. 12 (1). https://doi.org/10.1038/s41598-022-04982-w (2022).

Wu, X., Saxena, V., Zhu, K. & Balagopal, S. A CMOS spiking neuron for brain-inspired neural networks with resistive synapses and in situ learning. IEEE Trans. Circuits Syst. II Expr Brie. 62 (11), 1088–1092. https://doi.org/10.1109/tcsii.2015.2456372 (2015).

Nugroho, P., Leelarasmee, E. & Fujii, N. Tuning analysis of a CMOS current controlled ring oscillator. In 21st Int. Tech. Conf. Circuits/Systems Comput. Commun, 49–52 (2006).

Feldman, A., Nechushtan, O. & Shor, J. Voltage level detection for near-Vth computing. IEEE J. Solid-State Circ. 59, 1847–1857. https://doi.org/10.1109/JSSC.2023.3309865 (2024).

Wijekoon, J. H. B. & Dudek, P. Compact silicon neuron circuit with spiking and bursting behavior. Neural Netw. 21, 524–534. https://doi.org/10.1016/j.neunet.2007.12.037 (2008).

Livi, P. & Indiveri, G. A current-mode conductance-based silicon neuron for address-event neuromorphic systems. In 2009 IEEE Int. Symp. Circ. and Syst., 2898–2901. https://doi.org/10.1109/iscas.2009.5118408 (2009).

Sourikopoulos, I. et al. A 4-fJ/spike artificial neuron in 65 Nm CMOS technology. Front. Neurosci. 11. https://doi.org/10.3389/fnins.2017.00123 (2017).

Yue, K., Wang, X., Jadav, J., Vartak, A. & Parker, A. C. Analog neurons that signal with spiking frequencies. In Proc. Int. Conf. Neuromorphic Syst., 1–8. https://doi.org/10.1145/3354265.3354273 (2019).

Zare, M., Zafarkhah, E. & Anzabi-Nezhad, N. S. An area and energy efficient LIF neuron model with spike frequency adaptation mechanism. Neurocomput 465, 350–358. https://doi.org/10.1016/j.neucom.2021.09.004 (2021).

Quan, J., Liu, Z., Li, B. & Luo, J. Ultra-low-power compact neuron circuit with tunable spiking frequency and high robustness in 22 nm FDSOI. Electron 12 (12), 2648. https://doi.org/10.3390/electronics12122648 (2023).

Quan, J., Liu, Z., Li, B., Zeng, C. & Luo, J. 55 Nm CMOS mixed-signal neuromorphic circuits for constructing energy-efficient reconfigurable SNNs. Electron. 12 (19), 4147. https://doi.org/10.3390/electronics12194147 (2023).

Siddique, R., Eftimie, M. & Banad, Y. M. A comparative analysis of neuromorphic neuron circuits for enhanced power efficiency and spiking frequency in 22nm CMOS technology. 2024 IEEE 67th Int. Midw. Sym. Circ. and Syst. (MWSCAS), 1096–1100. https://doi.org/10.1109/mwscas60917.2024.10658829 (2024).

Singh, A., Kim, D., Lee, H. & Lee, B. G. A high-frequency CMOS meminductor emulator for spiking neuron. IEEE Trans. Circ. Syst. I Reg. Pap. 72 (3), 1056–1067. https://doi.org/10.1109/tcsi.2024.3454553 (2024).

MS, D., Raghu, H. R. S., SB, R. & J., & Simulation-based effective comparative analysis of neuron circuits for neuromorphic computation systems. Neurocomput. 614, 128758, 1–12. https://doi.org/10.1016/j.neucom.2024.128758 (2025).

Tanaka, G., Matsumori, T., Yoshida, H. & Aihara, K. Reservoir computing with diverse timescales for prediction of multiscale dynamics. Phys. Rev. Resea. 4 (3). https://doi.org/10.1103/physrevresearch.4.l032014 (2022).

Lee, Y., Seong, T., Yoo, S. & Choi, J. A low-jitter and low-reference-spur ring-VCO-based switched-loop filter PLL using a fast phase-error correction technique. IEEE J. Solid-State Circ. 53 (4), 1192–1202. https://doi.org/10.1109/jssc.2017.2768411 (2018).

Ho, Y., Yang, Y., Chang, C. & Su, C. A near-threshold 480 mhz 78 µW all-digital PLL with a bootstrapped DCO. IEEE J. Solid-State Circ. 48 (11), 2805–2814. https://doi.org/10.1109/jssc.2013.2280409 (2013).

Zhang, Y., Rhee, W., Kim, T., Park, H. & Wang, Z. A 0.35–0.5-V 18–152 MHz digitally controlled relaxation oscillator with adaptive threshold calibration in 65-Nm CMOS. IEEE Trans. Circ. Syst. II Expr Brie. 62 (8), 736–740. https://doi.org/10.1109/tcsii.2015.2433531 (2015).

Zhu, Z. & Feng, L. A review of sub-µW CMOS analog computing circuits for instant 1-dimensional audio signal processing in always-on edge devices. IEEE Trans. Circ. Syst. I Reg. Pap. 71 (9), 4009–4018. https://doi.org/10.1109/tcsi.2024.3408819 (2024).

Zhang, H. & Wang, Y. A 5.27nW/kHz low power relaxation oscillator with current consumption reduction technique. 2024 IEEE 7th Adv. Info. Tech., Electro. and Auto. Contr. Conf. (IAEAC), Chongqing, China., 1336–1339. https://doi.org/10.1109/IAEAC59436.2024.10503920 (2024).

Tanaka, G. et al. Recent advances in physical reservoir computing: A review. Neural Netw. 115, 100–123. https://doi.org/10.1016/j.neunet.2019.03.005 (2019).