AI chip design startup Verkor.io claims, in a research paper published in March, that its agentic AI system, Design Conductor, autonomously produced a complete RISC-V CPU core — taking a 219-word requirements document and generating a verified, layout-ready design in 12 hours, which is orders of magnitude faster than the standard 18- to 36-month timelines seen in commercial chip design.

Go deeper with TH Premium: AI and data centers

(Image credit: Microsoft)

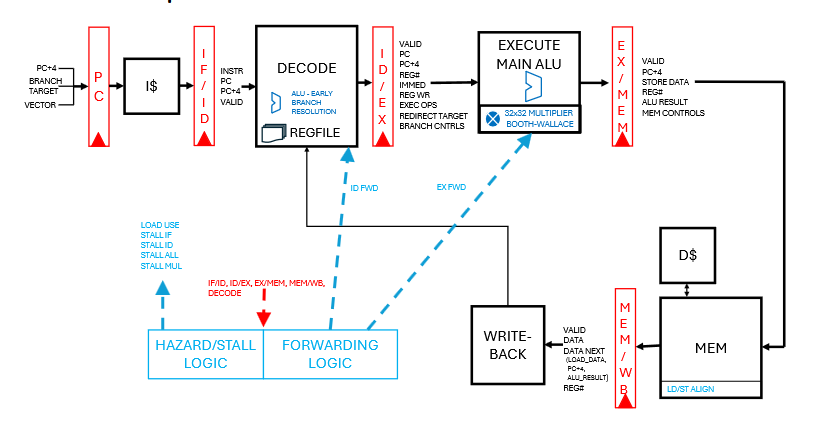

Verkor’s paper goes into detail on the pipeline architecture, which includes instruction fetch, decode, execute, memory, and writeback stages with early branch resolution and operand forwarding.

A five-stage in-order core with no caches and no out-of-order execution is a fairly straightforward design by industry standards. Verkor’s own paper notes that leading-edge chips cost north of $400 million and take 18 to 36 months with engineering teams in the hundreds, but VerCore is far simpler than those designs. That said, the 12-hour timeline is still notable for a fully autonomous run from spec to layout, even if it did require “many tens of billions of tokens” at this comparatively pale level of complexity.

Article continues below

You may like

(Image credit: Verkor.io)

VerCore hasn’t been physically fabricated and was instead verified in simulation using Spike, a reference RISC-V ISA simulator, and ASAP7 is an academic process design kit, not a production 7nm node. Verkor says it can run a uCLinux variant in simulation.

Verkor’s paper is candid about the limitations of the underlying language models, admitting that the agent sometimes “underestimates the complexity of work that is required to address certain issues.” For example, in one case, when failing to meet timing, Design Conductor tried to make major changes to “deepen the pipeline, instead of looking for simpler explanations.”

In another case, the researchers observed the model reasoning about Verilog, an event-driven language, as if it were sequential code. “While we found that this did not impact DC’s ability to achieve functional correctness, it made it more challenging for DC to debug timing issues,” the researchers explained.

The researchers estimate that five to 10 human experts will still be required to guide the system toward a production-ready chip. In addition, compute requirements grow non-linearly as design complexity increases, which makes the whole process less practical on a commercial scale. Verkor said it plans to release VerCore’s RTL source and build scripts by the end of April, and the company also intends to showcase an FPGA implementation at DAC (the annual Electronic Design Automation Conference).

Previous AI chip design efforts, such as the Chinese researchers who produced a RISC-V CPU in under five hours in 2023 and the more recent QiMeng project, used different methodologies and architectures. Verkor’s Design Conductor handles the full design process from spec to GDSII autonomously, though it shares the same limitation that all other AI-designed chips have: no physical silicon.

Follow Tom’s Hardware on Google News, or add us as a preferred source, to get our latest news, analysis, & reviews in your feeds.