Intel plans virtual “super processor cores”

Intel has applied for patents for “software-defined supercores” (SDC) in several countries. This involves several slim CPU cores cooperating for higher single-threading performance when required. This is apparently intended to solve a well-known dilemma for CPU developers: For maximum single-threaded performance, a CPU core needs as many computing units that can be used in parallel as possible. However, such a “wide” core takes up a lot of silicon space and draws a lot of power at high clock frequencies. For high multi-threaded computing performance, on the other hand, many compact cores can be more favorable.

Familiar idea, newly implemented

The idea of using several compact computing units in parallel if required has already been implemented. In Zen cores up to the Zen 4 generation, AMD connects two AVX2 computing units, each 256 bits wide, in order to process AVX 512 instructions.

A more general concept is the Coarse-Grain Reconfigurable Array (CGRA), which interconnects a certain number of small execution units depending on the computing task.

Conversely, there have also been processors in which two cores share certain computing units, such as the AMD Bulldozer architecture with “Shared FPU”.

SDC details

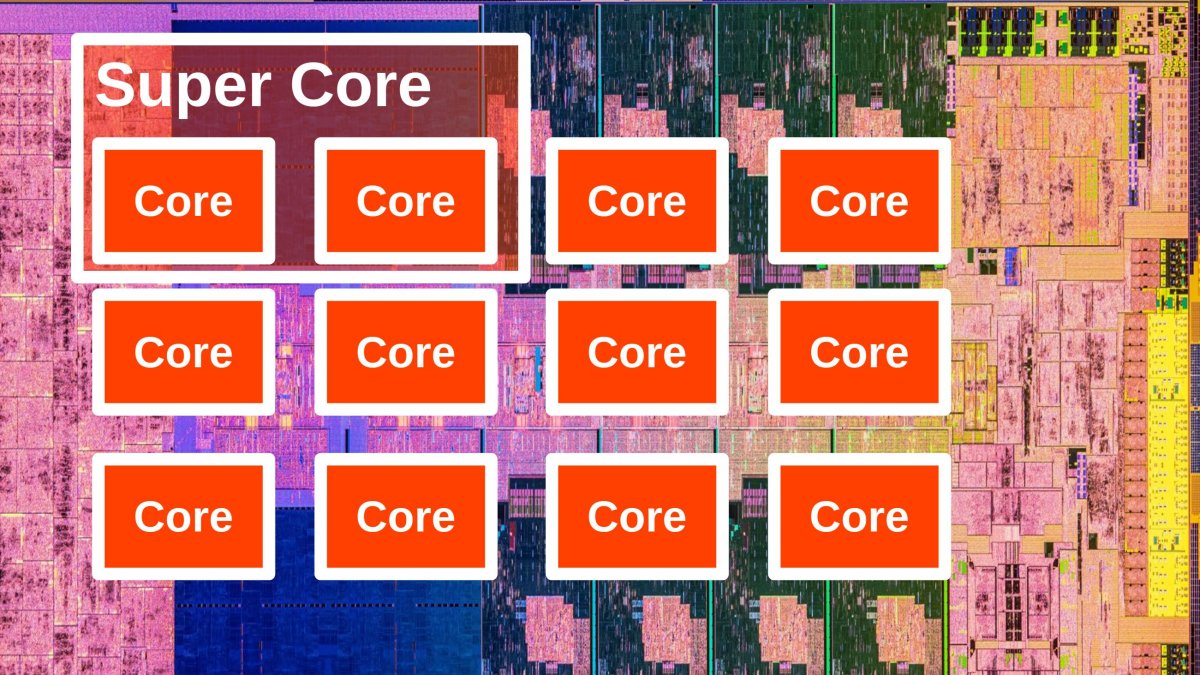

Software-defined supercores: two cores share the workload

(Image: Intel, US-Patentanmeldung US20250217157A1, Google)

In patent application US20250217157A1, Intel explains the functionality of a software-defined supercore in more detail. For example, two cores could work together as an SDC to process a single thread faster. Flow control instructions in the code provide information on which code sections should be processed in parallel if possible.

According to the patent application, relatively little additional hardware is required in each core for this cooperation to work efficiently.

Solution to the P-core problem?

If you compare current x86 processors from AMD and Intel, you will notice that Intel’s performance (P) cores take up a relatively large amount of space. Intel’s efficiency cores (E-cores) are much more compact, with an area ratio of almost four to one. With single-threading, however, the E-cores are significantly weaker than the P-cores. Dynamically combinable, slimmer cores could provide a remedy.

AMD has so far not used E-cores in this sense, but more compact and efficient Zen cores with the same range of functions (Zen 5/5c).

AMD and Intel are planning several innovations to the x86 architecture. They joined forces in fall 2024 to form the x86 Ecosystem Advisory Group (EAG). According to a post by AMD Vice President Robert Hormuth on LinkedIn, the x86 partners have agreed on FRED, AVX10 and APX, among other things.

Flexible Return and Event Delivery (FRED) is an updated concept for processing interrupts. AVX10 and the Advanced Performance Extensions (APX) reorganize the AVX versions and bring, among other things, twice as many registers. Intel’s Nova Lake, which is expected to arrive at the end of 2026 as the Core Ultra 400 for LGA1954 boards, could be the first Intel CPU with APX and AVX10.2.

(ciw)

Don’t miss any news – follow us on

Facebook,

LinkedIn or

Mastodon.

This article was originally published in

It was translated with technical assistance and editorially reviewed before publication.

Dieser Link ist leider nicht mehr gültig.

Links zu verschenkten Artikeln werden ungültig,

wenn diese älter als 7 Tage sind oder zu oft aufgerufen wurden.

Sie benötigen ein heise+ Paket, um diesen Artikel zu lesen. Jetzt eine Woche unverbindlich testen – ohne Verpflichtung!